- 411.47 KB

- 2022-05-11 18:36:29 发布

- 1、本文档共5页,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,可选择认领,认领后既往收益都归您。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细先通过免费阅读内容等途径辨别内容交易风险。如存在严重挂羊头卖狗肉之情形,可联系本站下载客服投诉处理。

- 文档侵权举报电话:19940600175。

华中科技大学电子线路设计与测试实验数字钟设计实验报告班级:自动化1505班姓名:李蓝鑫学号:U201514280

2017年5月一、实验目的1、掌握数字钟电路的设计与调试方法2、熟悉使用VERILOGHDL语言描述时序逻辑电路的方法,以及EDA仿真技术二、实验内容1、以数字形式显示时、分、秒的时间;2、小时计数器为同步24进制;3、要求手动校时、校分;4、任意时刻闹钟;5、小时显示(12/24)切换电路;6、仿广播电台正点报时。三、模块化,层次化设计(框图设计)秒译码显示部分分钟译码显示部分小时译码显示部分二选一模块选择闹钟与计时译码

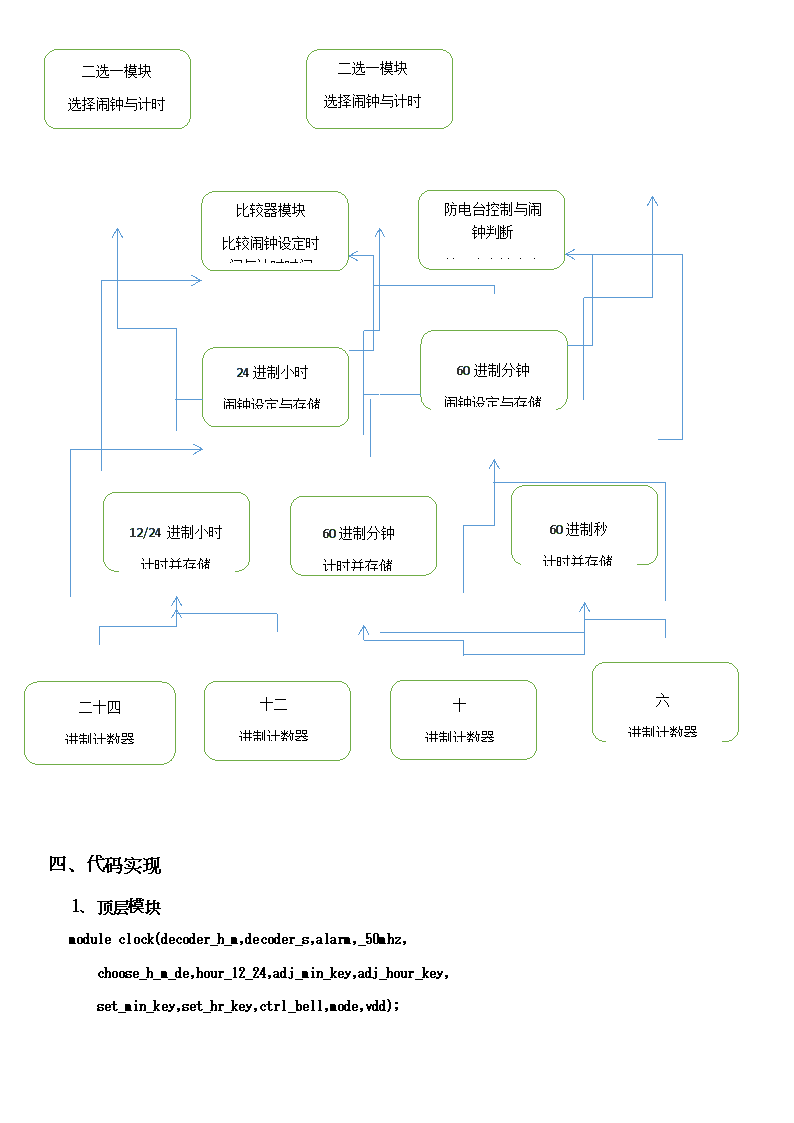

二选一模块选择闹钟与计时译码二选一模块选择闹钟与计时译码防电台控制与闹钟判断以及声音输出电路比较器模块比较闹钟设定时间与计时时间60进制分钟闹钟设定与存储24进制小时闹钟设定与存储60进制分钟计时并存储12/24进制小时计时并存储60进制秒计时并存储十进制计数器六进制计数器十二进制计数器二十四进制计数器一、代码实现1、顶层模块moduleclock(decoder_h_m,decoder_s,alarm,_50mhz,choose_h_m_de,hour_12_24,adj_min_key,adj_hour_key,set_min_key,set_hr_key,ctrl_bell,mode,vdd);

input_50mhz;//DE0实验板上的晶振频率wire_1khzin,_1hz,_2hz,_500hz;//分频器的输出信号,1khz通过不同位权的二进制数字获得1hz,2hz,500hz的输出信号inputvdd;//用于提供整个数字钟的异步清零端或者高电平电压,0时清零wire[7:0]hour,minute,second;//计时器的输出信号,作为中间变量存储和传输时间信号wire[7:0]hour_12,hour_all;//12进制的小时计数器的变量,hour_all表示把12进制和24进制用一个变量统一,便于译码inputadj_min_key,adj_hour_key;//校正计时器小时分钟的输入按键,为1时校正时间,为0时正常计时//计时器的中间使能控制信号,用于计时器的扩展,比如分进位用于控制小时的计数,实现模拟数字钟计时功能wireminl_en,minh_en,hour_en;inputhour_12_24;//12进制与24进制的显示切换,也就是选择hou还是hour_12当为1时12进制,为0时是24进制表达regalarm_radio;//仿电台的报时信号输出,当此信号为1时报时信号输出,当此信号为0时不输出wirealarm_clock;//闹钟的信号输出,同仿电台报时的功能,当此信号为1时,闹钟信号输出inputctrl_bell;//控制闹钟的声音是否输出的按键outputalarm;//仿电台报时或者闹钟声音信号的输出,集成在一个输出端口,采用或运算使之输出在一起wire[7:0]set_hr,set_min;//设定的闹钟时间输出信号,用于用户设置闹钟定时和用于和当前计时器的时间比较inputset_hr_key,set_min_key;//设定闹钟小时和分钟的输入按键,作为小时计数器和分钟计数器的使能信号

//如果按下,使能有效,正常递增,当松开时,使能无效,不再递增,保存当前的值为闹钟所设定的时间。//闹钟设定时间和计时器比较器的结果输出,分别为小时的十位比较结果//小时个位比较结果,分钟十位比较结果,分钟个位比较结果wirehr_h_equ,hr_l_equ,min__h_equ,min_l_equ;inputchoose_h_m_de;//因4个数码管显示限制,用于控制显示小时还是分钟信号,1表示小时,0表示分钟output[13:0]decoder_h_m,decoder_s;//译码器的输出,也就是小时、分、秒的译码,用于控制七段译码管的亮灭wire[7:0]led_hr,led_min,led_sec;//输出8421BCD码给显示器,时分秒都是两位十进制数表示,需要八位二进制的BCD二进制码来表示wire[7:0]led_min,led_sec;//说明变量的类型wire[7:0]led_h_min;//由于译码管数量限制,所以把计时的时分集中在一个变量里便于译码inputmode;//设定显示器的显示模式,MODE=1时,显示闹钟所设定的时间,反之则显示计时器的时间//50MHZ分频器调用模块,50mhz为DE0实验板上的晶振频率divided50mhzde1(_1khzin,vdd,_50mhz);//1khz分频器的模块调用,vdd,作为使能信号和清零信号,都处于高电平状态。前三种频率的信号为分频输出divided_frequencyu0(_1hz,_2hz,_500hz,vdd,vdd,_1khzin);//60进制秒计数器:调用10进制和6进制底层模块构成counter10u1(second[3:0],vdd,vdd,_1hz);//秒个位计数器,为十进制,使能信号接电源高电平,一直有效,即一直计数,符合秒的概念

counter6u2(second[7:4],vdd,(second[3:0]==4"h9),_1hz);//秒计数器十位计数器,以秒个位是否达到九作为使能控制信号//也就是个位是否产生进位,也就实现了60进制的扩展assignminl_en=adj_min_key?vdd:(second==8"h59);//分钟的个位使能信号产生,adj_min_key为1时校正分钟信号,所以无需等待秒的进位//而为0时,则是正常计时状态,虚等待秒的进位来充当使能信号,产生正常的分钟计数assignminh_en=(adj_min_key&&(minute[3:0]==4"h59))||(mintue[3:0]==4"h9)&&(second==8"h59);//分钟的十位使能信号产生,adj_min_key为1时校正分钟信号//但此时即便在校正状态,也需等待分钟信号的个位进位信号//当其为0时,分钟是正常即使状态,需同时满足秒的进位与分钟的个位进位//60进制分钟计数器,也是调用十进制计数器与6进制计数器完成,与秒计数器所不同的是使能信号的不同counter10u3(mintue[3:0],vdd,minl_en,_1hz);//分计数器的个位计数counter6u4(mintue[7:4],vdd,minh_en,_1hz);//分计数器的十位计数//产生小时计数器使能信号//为1时校正小时,为0时正常计时,由于小时直接采用底层的24进制计数器//所以只有一个使能信号,无需十位与个位的使能信号相区分//正常计数时,需同时满足秒的进位与分的进位assignhour_en=adj_hour_key?vdd:((mintue==8"h59)&&(second==8"h59));//调用24进制计数器进行小时计数counter24u5(hour[7:4],hour[3:0],vdd,hour_en,_1hz);//24进制小时计数器//调用12进制计数器进行小时计数counter12u6(hour_12[7:4],hour_12[3:0],vdd,hour_en,_1hz);//12进制小时计数器

//仿电台整点报时功能always@(minuteorsecond)//因为每逢整点都要报时。所以无需引入小时hour信号if(minute==8"h59)//先判断分钟计数器是否满足59,再进行判断秒计数器的数值case(second)//由于需要在51,53,55,57,59秒时报时,所以用case语句8"h51,8"h53,8"h55,8"h57:alarm_radio==_500hz;//当出现51,53,55,57,时都往下来执行输出500HZ的信号语句8"h59:alarm_radio==_1khzin;//当出现59秒时,开始输出1000HZ的信号语句default:alarm_radio=1"b0;//其他情况下输出0,也就是不报时endcaseelsealarm_radio=1"b0;//当分钟信号不满足59时输出为0,也就是不输出报时信号//闹钟设定模块//60进制分计数器,用于闹钟设定分钟counter10su1(set_min[3:0],vdd,set_min_key,_2hz);//当设置分钟的按键按下时使能信号有效,开始计数递增//松开时,设定的分钟个位信号存入闹钟数字存储的低4位BCD码counter6su2(set_min[7:4],vdd,(set_min[3:0]==4"h9),_2hz);//分钟的十位设置//24进制小时计数器,用于闹钟设定小时counter24su3(set_hr[7:4],set_hr[3:0],vdd,set_hr_key,_2hz);//此时,设定小时的按键充当使能信号//比较闹钟时间和计时器设定时间是否相等_4bitcomparersu4(hr_h_equ,set_hr_[7:4],hour[7:4]);//调用4位比较器,一次比较一个BCD码表示的十进制数字_4bitcomparersu5(hr_l_equ,set_hr_[3:0],hour[3:0]);//小时的个位比较结果_4bitcomparersu6(min_h_equ,set_min_[7:4],minute[7:4]);//分钟的十位比较结果_4bitcomparersu7(min_l_equ,set_min_[3:0],minute[3:0]);//分钟的个位比较结果

//闹钟声音控制信号assignalarm_clock=ctrl_bell?(((hr_h_equ&&hr_l_equ&&min_h_equ&&min_l_equ))&&(((second[0]==1"b1)&&_500hz)||((second[0]==1"b0)&&_1khzin)):1"b0;//当CTRL_BELL为1时,闹钟声音被允许输出,才进行后续判断,而为0时,不允许输出,时钟为0;//hr_h_equ&&hr_l_equ&&min_h_equ&&min_l_equ)用于检测是否满足闹钟响铃条件//即设定时间与当前时间是否相等。//second[0]==1"b1)&&_500hz)||((second[0]==1"b0)&&_1khzin)用于给闹钟输出信号变量赋值//500hz和1khz交替输出,用秒的最低位一直在0和1跳变来实现。//把声音输出模块集成在一起,报时和闹钟信号assignalarm=alarm_radio||alarm_clock;//2选一模块用于选择显示12进制小时还是24进制小时_2to1muxmu0(hour_all,hour_12_24,hour_12,hour);//选择显示闹钟时间还是正常计时的时间_2to1muxmu1(led_hr,mode,set_hr,hour_all);_2to1muxmu2(led_min,mode,set_min,minute);_2to1muxmu3(led_sec,mode,8"h00,second);//用于选择是显示小时还是分钟_2to1muxmu4(led_h_min,choose_h_m_de,led_hr,led_min);//七段译码器模块调用decoderde2(led_h_min,decoder_h_m);//译码小时和分钟的集成decoderde3(led_sec,decoder_s);//译码秒的计数endmodule

2、二选一模块//二选一模块完成模式选择module_2to1mux(out,sel,x,y);input[7:0]x,y;//声明模块内使用变量,用于接收小时与分钟的BCD码inputsel;//选择信号output[7:0]out;//输出信号assignout=sel?x:y;//用选择语句完成,为1时赋值XEndmodule3、四位比较器模块//4位比较器模块module_4bitcomparer(equ,a,b);input[3:0]a,b;//声明模块内使用变量,用于接收待比较1位十进制数的BCD码outputequ;//输出变量,比较结果存储在此变量中,相等为1,不相等为0assignequ=(a==b);Endmodule4、分频器模块(1)、1KHZ分频到500hz,4hz,1hz模块moduledivided_frequency(_1hzout,_2hzout,_500hzout,ncr,en,_1khzin);input_1khzin,ncr,en;output_1hzout,_2hzout,_500hzout;//分频器的结果输出,即不同频率的信号wire[11:0]q;//用于获取分频信号的变量,在不同位上取,就可获得不同的频率信号wireen1,en2;//使能信号//通过使用三个十进制计数器完成1000进制的计数器扩展counter10du0(q[3:0],ncr,en,_1khzin);counter10du1(q[7:4],ncr,en1,_1khzin);counter10du3(q[11:8],ncr,en2,_1khzin);assignen1=(q[3:0]==4"d9);

assignen2=(q[7:4]==4"d9)&(q[3:0]==4"d9);assign_1hzout=q[11];assign_2hzout=q[10];assign_500hzout=q[0];//最低位实现二分频,位往高位移动,依次类推Endmodule(2)、50MHZ分频到1khz模块moduledivided50mhz(_1khzin,ncr,_50mhz);input_50mhz,ncr;//异步清零端outputreg_1khzin;reg[15:0]q;//用于存储计数数字always@(posedge_50mhz,negedgencr)beginif(~ncr)//异步清零beginq<=15"d0;_1khzin<=1"b0;end//当计数到24999时,1khz变量翻转,因为50mhz频率是1000hz的50000倍elseif(q==15"b110000110100111)Begin//所以1khz的周期是50mhz的50000倍,24999个周期翻转一次,翻转两次构成q<=15"d0;//一个周期,恰好满足50000倍的周期关系,也就达到分频的效果_1khzin<=(~_1khzin);endelsebeginq<=q+1"b1;//正常加1endendendmodule

5、十进制模块modulecounter10(q,ncr,en,cp);inputcp,ncr,en;output[3:0]q;//输出变量reg[3:0]q;always@(posedgecp,negedgencr)//上升沿出发的时钟脉冲信号,下降沿出发的异步清零信号beginif(~ncr)q<=4"b0000;//异步清零elseif(~en)q<=q;//当使能为0时,暂停计数,保持原来的数值elseif(q==4"b1001)q<=4"b0000;//当数字到达第十个状态,也就是九时再次清零,完成一次十进制计数elseq<=q+1"b1;//正常计数endEndmodule6、六进制模块//6进制计数器modulecounter6(q,ncr,en,cp);inputcp,ncr,en;output[3:0]q;reg[3:0]q;always@(posedgecp,negedgencr)beginif(~ncr)q<=4"b0000;elseif(~en)q<=q;elseif(q==4"b0101)q<=4"b0000;//与十进制所不同的就是清零的状态不同elseq<=q+1"b1;endEndmodule7、二十四进制模块

//24进制计数器,用于小时计数modulecounter24(cnth,cntl,ncr,en,cp);inputcp,ncr,en;//时钟脉冲,与异步清零信号和使能信号output[3:0]cnth,cntl;//24的十位和个位的BCD码表示reg[3:0]cnth,ctnl;always@(posedgecp,negedgencr)beginif(~ncr){cnth,cntl}<=8"h00;//异步清零elseif(~en){cnth,cntl}<={cnth,cntl};//使能为01时保持原有状态elseif((cnth>2)||(cntl>9)||((cnth==2)&&(cntl>=3))){cnth,cntl}<=8"h00;//当满足十位大于2,个位大于9,整体大于23时,都属于越界的情况都需要清零elseif((cnth==2)&&(cntl<3))//当十位为2,个位小于3时,个位正常加1begincnth<=cnth;cntl<=cntl_1"b1;endelseif(cntl==9)//个位为9时,需要进位,然后个位再清零begincnth<=cnth+1"b1;cntl<=4"b0000;endelsebegincnth<=cnth;cntl<=cntl_1"b1;end//其他情况也是个位正常加1,十位保持原状endEndmodule5、十二进制模块modulecounter12(cnth,cntl,ncr,en,cp);inputcp,ncr,en;output[3:0]cnth,cntl;reg[3:0]cnth,cntl;always@(posedgecp,negedgencr)beginif(~ncr){cnth,cntl}<=8"h00;elseif(~en){cnth,cntl}<={cnth,cntl};elseif((cnth>1)||(cntl>9)||((cnth==1)&&(cntl>=1))){cnth,cntl}<=8"h00;//与24进制所不同之处在于十位是1的时候开始复位

elseif((cnth==1)&&(cntl<1))begincnth<=cnth;cntl<=cntl+1"b1;endelseif(cntl==9)begincnth<=cnth+1"b1;cntl<=4"b0000;endelsebegincnth<=cnth;cntl<=cntl+1"b1;endendendmodule5、七段译码管模块moduledecoder(number,num_decoder);input[7:0]number;//需要被译码的两位十进制数的BCD码outputreg[13:0]num_decoder;//译码输出变量,直接控制七段译码管的亮与灭always@(number,num_decoder)begincase(number[7:4])//十位译码,DE0实验板上的显示管是共阳极,为0时亮4"d0:num_decoder[13:7]=7"b0000001;4"d1:num_decoder[13:7]=7"b1001111;4"d2:num_decoder[13:7]=7"b0010010;4"d3:num_decoder[13:7]=7"b0000110;4"d4:num_decoder[13:7]=7"b1001100;4"d5:num_decoder[13:7]=7"b0100100;4"d6:num_decoder[13:7]=7"b0100000;4"d7:num_decoder[13:7]=7"b0001111;4"d8:num_decoder[13:7]=7"b0000000;4"d9:num_decoder[13:7]=7"b0000100;default:num_decoder[13:7]=7"b1111111;endcasecase(number[3:0])//个位译码4"d0:num_decoder[6:0]=7"b0000001;

4"d1:num_decoder[6:0]=7"b1001111;4"d2:num_decoder[6:0]=7"b0010010;4"d3:num_decoder[6:0]=7"b0000110;4"d4:num_decoder[6:0]=7"b1001100;4"d5:num_decoder[6:0]=7"b0100100;4"d6:num_decoder[6:0]=7"b0100000;4"d7:num_decoder[6:0]=7"b0001111;4"d8:num_decoder[6:0]=7"b0000000;4"d9:num_decoder[6:0]=7"b0000100;default:num_decoder[6:0]=7"b1111111;endcaseendendmodule五、模块功能仿真1、二选一模块

Sel为选择信号当sel=1时,选择x信号,x全为1当sel=0时,选择Y信号,y全为0比如这一列:a为1010b为0101所以a>b,则输出不想等equ变量即为02、四位比较器模块此为500hz分频结果前面一部分使能无效,没有计数满足周期的2倍关系3、1KHz分频器模块

此部分是分频为2hz的结果由图可知2hz的输出的周期为1000ns满足于1khz的周期为2ns的500倍关系由图可知,10进制0开始到9一共10个状态循环计数4、十进制模块5、六进制模块

从0到11变化,12个状态周期变化,个位、十位分开表示从0到5变化,6个状态周期变化6、十二进制模块从0到23变化,24个状态周期变化,个位、十位分开表示7、二十四进制模块

输出周期(1us)与输入周期(20ps)之间满足50000倍关系、分频成功8、50MHz分频模块以此列低位为例当个位数字表示4时译码为1001100,满足显示要求9、译码器模块五、数字钟整体功能仿真1、说明(1)、以闹钟为示例,因为闹钟基本覆盖所用功能(2)、50mhz的分频功能暂时屏蔽,节省仿真时间(3)、采用前一段设置闹钟时间,接着一段校正时间,基本校正到与闹钟时间相同,而后再正常计时,产生一分钟闹钟的输出。

这一段表示对时间的校正脉冲频率是1hz,持续时间为设置闹钟的时间的两倍,这样得到的时间与闹钟相同2、波形这一段表示闹钟响铃因为计时的时分与闹钟的时分恰好相等,而持续60s后,分钟不相同闹钟消失这是秒的译码输出满足60一循环即高位6个循环低位10个循环图示满足功能要求这一段表示设置闹钟时间脉冲频率为2hz

五、实验总结1、调试收获(1)、50mhz分频到1khz的代码实现问题首先,50mhz到1khz有50000倍的频率关系,反过来就有50000的周期关系;其次,由于是上升沿触发,所以一个周期只能触发一次,也就是计数一次,所以,当计数为1时,即过了一个周期。最后,每25000个状态时翻转一次,那么50000个状态后就构成输出变量的一个周期,则恰好满足周期的50000倍关系,也就达到了分频的目的(2)、时分的显示问题由于DE0实验板的只有四个八段译码管,所以分和时的显示只能集成带两个译码管上,用一个拨码开关来进行切换。也可以采用发光二极管来显示秒的计数,八位二进制数分别控制八个发光二极管的亮与灭。(3)、波形仿真相关问题在纠正了一些代码的低级语法错位之后,波形仿真各个部分都没有问题,但整体仿真时却始终不出正确结果波形。经反复查证,发现在VDD部分的设置初始值时在前一段设置了低电平之后,在很长一段之后又出现了低电平,也就相当于产生了清零,隔一段时间清零,当然也就不能完成指定的功能;除此之外,还出现了时分秒的输出在波形上的显示的数字递增规律不对,从28以后就直接乱变化了,后来明白,其次时分秒的高四位和低四位并不满足2进制数的规律,因为是十进制关系,所以当28以后的波形仍然是正确的,但是显示的数字却不是单纯的八位二进制数。另外,在数字钟整体进行仿真时,仿真时间极其漫长,甚至几个小时,其实后来一想,不用再分频模块太过于校正,分频模块单独验证功能正确之后,完全可以在整体仿真时屏蔽掉,这样会节省很多仿真时间,因为分频也只是为了得到一个频率的信号,可以直接给定,这样可以快速有效得验证其他功能。

(4)、其他问题也就是一些大妈撰写过程中出现的低级错误,在编译过程中会会报出各种错,当然有些错误我并不懂,只能上网查证,这个纠错过程其实很愉快也很有收获,比如少分号,大小写,没有变量声明。2、总结耐烦一点什么都好啦,坚持就是胜利,哈哈哈!

八、数字钟功能表功能输入变量输出变量Modectrl_bellVDD_50mhzchoose_h_m_dehour_12_24adj_min_keyadj_hour_keyset_min_keyset_hr_keyalarmdecoder_h_mdecoder_s备注:选择数码管显示内容,1显示闹钟设定时间,0显示正常计时(用拨码开关)D2备注:控制闹钟信号输出,1表示允许输出(使用拨码开关)E4备注:作为整个架构中的高电平输入(使用拨码开关,拨至高电平)E3备注:DE0实验板上50mhz晶振频率(使用50MHZ频率输入端口)G21备注:因4个数码管显示限制,用于控制显示小时还是分钟信号,1表示小时,0表示分钟(使用拨码开关)H7备注:12进制与24进制的显示切换,当为1时12进制,为0时是24进制表达(使用拨码开关)J7备注:校正分钟的控制信号,为1时,开始校正,直接递增(使用拨码开关)G5备注:校正小时的控制信号,为1时开始校正时间,直接递增(使用拨码开关)G4备注:用于控制闹钟分钟信号是否开始设置为1时开始递增,为0时保持原状(使用拨码开关)H6备注:用于控制闹钟小时信号是否开始设置为1时开始递增,为0时保持原状(使用拨码开关)H5闹钟信号(不同频率输出)和报时信号(1khz)的集成输出输出(使用二极管)J1七段译码管小时和分钟的集成输出(分配到两个七段译码管端口)七段译码管秒的集成输出(分配到两个七段译码管端口)24进制计时0050MHZ0/MIN1/HOUR00000无输出

基本计时功能(前一小段0用于各项清零)1相应正常计时时/分信号相应正常计时秒信号12进制计时00(前一小段0用于各项清零)150MHZ0/MIN1/HOUR10000无输出相应正常计时时/分信号相应正常计时秒信号校正时间功能00(前一小段0用于各项清零)150MHZ0/MIN1/HOUR01100无输出一直递增的时/分信号正常计时的秒信号设置闹钟时间1050MHZ0/MIN1/HOUR00011无输出显示设置的闹钟时/分信号显示00

任意时刻闹钟功能(前一小段0用于各项清零)1验证闹钟输出01(前一小段0用于各项清零)150MHZ0/MIN1/HOUR00000在达到对应设置的时分时,信号输出(闪一分钟)正常计时的时/分信号正常计时的秒信号仿电台报时功能01(前一小段0用于各项清零)150MHZ0/MIN1/HOUR00000满足分和秒的条件时电台报时信号输出特定秒时闪正常计时的时/分信号正常计时的秒信号

您可能关注的文档

- 66kV与以下架空电力线路设计规范标准[详].doc

- 临时用电线路设计方案.doc

- KV架空配电线路设计

- KV~KV架空输电线路设计规范(GB -) 强制性条文 word整理版

- 0KV架空线路设计施工方案

- 网上获取信息的策略旅游线路设计教学案例.doc

- GB50061-97 66KV及以下架空电力线路设计规范.doc

- 电力系统低压配电装置和线路设计方法.doc

- 电子线路设计实验报告 小学期课程设计.doc

- 旅游线路设计方案教学.doc

- 采区车场轨道线路设计.ppt

- 架空输电线路设计试卷.doc

- 线路设计员转正申请书.doc

- 10kV 配网线路设计软件备课讲稿.doc

- 智通地铁线路设计系统使用手册.doc

- 光缆线路设计培训(330).ppt

- 浅析10kV配电架空线路设计的要点.pdf

- 机床电气控制线路设计.ppt